芯片资讯

- 发布日期:2024-01-05 13:49 点击次数:122

1.先进制程贴近物理极限迭代放缓,Chiplet 展现集成优势

1.1.Chiplet 是延续摩尔定律的重要手段

Chiplet 俗称“芯粒”或“小芯片组”,通过将原来集成于同一 SoC 中的各个元件分拆,独立 为多个具特定功能的 Chiplet,分开制造后再通过先进封装技术将彼此互联,最终集成封装 为一个系统芯片。Chiplet 可以将一颗大芯片拆解设计成几颗与之有相同制程的小芯片,也 可以将其拆解设计成几颗拥有不同制程的小芯片。Chiplet 是一种硅片级别的 IP 整合重用技 术,其模块化的集成方式可以有效提高芯片的研发速度,降低研发成本和芯片研制门槛。 传统的 SoC 是将多个负责不同类型计算任务的计算单元,通过光刻的形式制作到同一块晶圆 上,其追求的是高度的集成化,利用先进制程对于所有的单元进行全面的提升。而 Chiplet 是在设计系统芯片时,先按照不同的计算单元或功能单元进行分解;然后针对每个单元选择 最适合的半导体制程工艺分别进行制造;再通过先进封装技术将各个单元彼此互联;最终集 成封装为一个系统级芯片组。

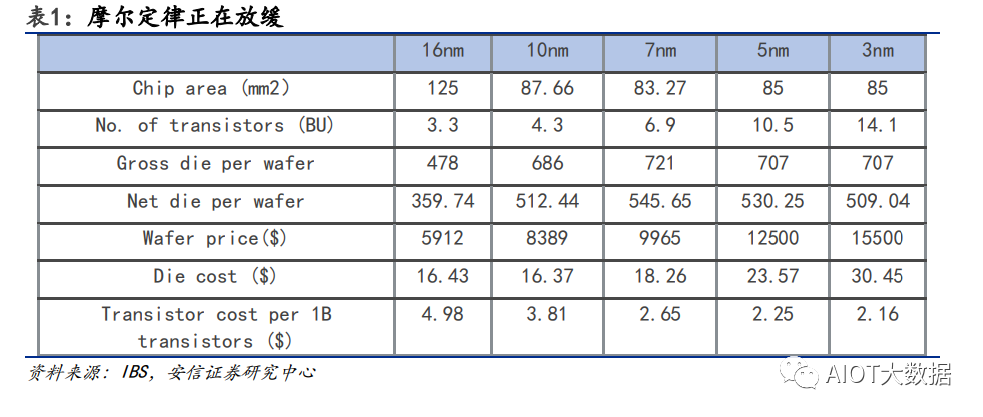

摩尔定律正在逐步放缓。随着工艺制程节点继续向着更小的 5nm、3nm 甚至埃米级别推进,半 导体工艺制程已经越来越逼近物理极限,不仅推进的难度越来越高,所需要付出的代价也越 来越大。研究机构 IBS 统计对比 16nm 至 3nm 的单位数量的晶体管成本指出,随着制程工艺 的推进,单位数量的晶体管成本的下降幅度在急剧降低。比如从 16nm 到 10nm,每 10 亿颗晶 体管的成本降低了 23.5%,而从 5nm 到 3nm 成本仅下降了 4%。随着先进制程的持续推进,单 位晶体管所需要付出的成本降低的速度正在持续放缓,即意味着摩尔定律正在放缓。 Chiplet 诞生背景是在摩尔定律放缓,性价比逐步凸显。摩尔定律由戈登·摩尔(Gordon Moore) 提出,其内容为“当价格不变时,集成电路上可容纳的晶体管的数目,约每隔 18-24 个月便 会增加一倍。”在集成电路过去几十年的发展过程中,受摩尔定律的指引,在晶体管的尺寸不 断微缩以及处理器性能不断增强的同时,半导体制程工艺的成本可以维持不变,甚至下降。 Chiplet 能够通过多个裸片片间集成,突破了单芯片 SoC 的诸多瓶颈,带来一系列优越特性, 从而延续摩尔定律。

1.2.Chiplet 在设计成本、良率、制造成本、设计灵活性等方面优势明显

与传统 SoC 相比,Chiplet 在设计成本、良率、制造成本、设计灵活性等方面优势明显。

1. Chiplet 能显著提升良率。在高性能计算、AI 等方面的巨大运算需求下,芯片性能快速 提升,芯片中的晶体管数量也在快速增加,导致芯片面积不断变大。对于晶圆制造工艺而言, 芯片面积越大,工艺的良率越低。由于每片 wafer 上都有一定概率的失效点,而对于晶圆工 艺来说,在同等技术条件下难以降低失效点的数量,因此被制造的芯片面积较大,失效点落 在单个芯片上的概率就越大,所以良率会下降。通过运用 Chiplet 的手段,可以将大芯片拆 解分割成几颗小芯片,单个芯片面积变小,失效点落在单个小芯片上的概率将大大降低,从 而提高了制造良率。

2. Chiplet 能降低芯片制造成本。Chiplet 的核心思想是先分后合,先将单芯片中的功能块 拆分出来,再通过先进封装模块集成为单芯片。将 SoC 进行 Chiplet 化之后,不同的芯粒可 以根据需要来选择合适的工艺制程分开制造,然后再通过先进封装技术进行组装,不需要全 部都采用先进的制程在一块晶圆上进行一体化制造,这样可以极大地降低芯片的制造成本。

3. Chiplet 能提高芯片设计的灵活度,显著降低设计成本。由于 Chiplet 芯粒可以独立设计 和组装,因此制造商可以根据自己的需要来选择不同类型、不同规格和不同供应商的芯粒进 行组合,很大程度上提高了芯片设计的灵活性和可定制化程度;并且制造商可以依赖于预定 好的芯片工具箱来设计新产品,缩短芯片的上市时间。同时 The Linley Group 在《Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small》中提出,Chiplet 技术可以将 大型 7nm 设计的成本降低高达 25%;在 5nm 及以下的情况下,节省的成本更大。

Chiplet 方案目前在互联与封装两块还存在一定的难点。Chiplet 的关键是让芯粒之间高速 互联,因此芯片设计公司在设计芯粒之间的互联接口时,需要保证高数据吞吐量与低数据延 迟和误码率,同时还要考虑能效和连接距离。Chiplet 方案对封装工艺也有更高的要求,主 要由于第一封装体内总热功耗将显著提升;第二芯片采用 2.5D/3D 堆叠,增加了垂直路径热 阻;第三更加复杂的 SiP,跨尺度与多物理场情况下热管理设计复杂。以上要求都给 Chiplet 技术的发展增加了难点。

2. AI 等高算力芯片的需求增加,Chiplet 迎来高速发展

2.1.Chiplet 在服务器中率先应用

在高性能计算领域,Chiplet 是满足当下对算力需求的关键技术。运用 Chiplet 技术,一方 面通过 Die to Die 连接和 Fabric 互联网络,能够将更多算力单元高密度、高效率、低功耗 地连接在一起,从而实现超大规模计算;另一方面,通过将 CPU、GPU 和 NPU 高速连接在同一 个 Chiplet 中,实现芯片级异构系统,可以极大提高异构核之间的传输速率,降低数据访问 功耗,从而实现高速预处理和数据调度;同时,其采用非先进制程构建 Cache(位于 CPU 与 内存之间的临时存储器),提高片上 Cache 的容量和性价比,并通过 3D 近存技术,降低存储 访问功耗,从而满足大模型参数需求。 从下游应用场景来看,服务器、自动驾驶领域是比较适合 Chiplet 落地场景,消费电子由于 对轻薄、功耗要求较高,不太适合应用 Chiplet。随着近年来高性能计算、人工智能、5G、 汽车、云端等新兴市场的蓬勃发展,对于算力的需求持续攀升,仅靠单一类型的架构和处理 器无法处理更复杂的海量数据,“异构”正在成为解决算力瓶颈关键技术方向。Chiplet 技术 目前主要聚焦于 HPC 高性能计算与 AI 人工智能领域,随着算力、存储等需求升级,Chiplet 有望在未来市场上得到更加广泛的应用。 国际巨头厂商已经布局 Chiplet 在高性能计算领域的应用。英特尔于 2022 年底发布了数据 中心 GPU Max,是英特尔针对高性能计算加速设计的第一款 3D GPGPU,在一颗芯片里集成了 47 颗芯粒,有 5 种制程,以此获得比上一代高出三倍性能的提升。

AMD 在这个方向走在了更前面,目前已经发布了第一个数据中心 APU(Accelerated Processing Unit,加速处理器)产品 MI300,其采用 Chiplet 技术,在 4 块 6 纳米芯片上, 堆叠了 9 块 5 纳米的计算芯片。AMD 表示,相较于上一代的 Instinct MI250,提升了 8 倍的 AI 训练算力和 5 倍的 AI 能效。 苹果则与台积电合作开发了 UltraFusion 封装技术,也是一种类似 Chiplet 的技术,能同时 传输超过 1 万个信号,芯片间的互连带宽可达 2.5TB/s,超出了 UCIe 1.0 的标准。苹果此前发布的 M1 Ultra 芯片将两个 M1 Max 芯片的裸片,采用 UltraFusion 封装技术进行互连,其 CPU 核心数量增加至 20 个,而 GPU 核心数量更是直接增加至 64 个。M1 Ultra 的神经网络引 擎也增加至 32 核,能够带来每秒 22 万亿次的运算能力。

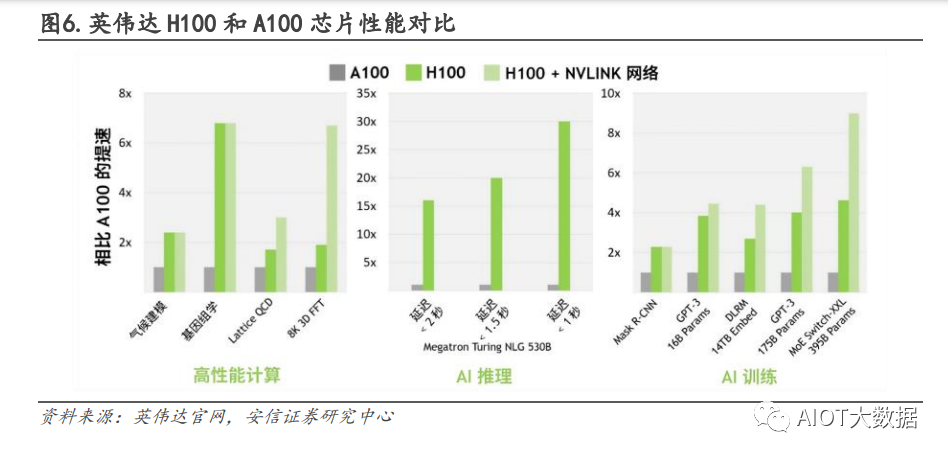

以 ChatGPT 为代表的的 AI 应用蓬勃发展,对上游 AI 芯片算力提出了更高的要求,而运用 Chiplet 模式的异构集成方案,可以通过将通用需求与专用需求解耦,大幅降低芯片设计投 入门槛及风险,有效解决下游客户在算法适配、迭代周期、算力利用率、算力成本等各方面 难以平衡的核心痛点。将支持人工智能的不同功能的芯片,如 GPU、CPU、加速器等,通过 Chiplet 的方式进行组合,可以构建出更高效的 AI 加速器系统。国际巨头厂商与国内领先厂 商均在 Chiplet 技术于 AI 芯片的运用做了不同突破。 英伟达使运用 Chiplet 技术制作 AI 芯片的领先企业,其于 2022 年发布的 H100 GPU 芯片就 是台积电 4nm 工艺和 Chiplet 技术融合的创新之作。英伟达通过 Chiplet 技术将 HBM3 显存 子系统集成到芯片里,可提供 3TB/s 的超高显存带宽,是上一代产品带宽的近两倍。同时借 助 4nm 先进制程,H100 GPU 芯片在 814 平方毫米的芯片面积里容纳 800 亿个晶体管,无论是 性能还是延迟,相较于上一代 A100 GPU 芯片都有巨大的提升。

英伟达另一款 AI 芯片 GH200 与 H100 属于同一际代,但应用场景有所不同。英伟达 H100 的 架构以 GPU 为主,重点用于数据运算和推理。GH200 架构采用 CPU+GPU 异构计算方式。GH200 采用 NVLink-C2C 技术方案,通过 Chiplet 工艺将基于 Arm 的 NVIDIA Grace CPU 与 NVIDIA H100 Tensor Core GPU 整合在了一起,实现流畅互连。具体来说,GH200 超级芯片将 72 核 的 Grace CPU、H100 GPU、96GB 的 HBM3 和 512 GB 的 LPDDR5X 集成在同一个封装中,拥有高 达 2000 亿个晶体管。这种组合提供了 CPU 和 GPU 之间高达 900G/s 的数据带宽,为某些内存 受限的工作负载提供了巨大的优势。相较 PCIe5,NVLink-C2C 在能效方面提升 25 倍,面积效 率提升 90 倍。

AMD 的 MI300 加速器也运用了 Chiplet 技术,是业内首款 CPU+GPU 异构计算的存算一体芯片。 MI300 加速器专为领先的高性能计算(HPC)和 AI 性能而设计,这款加速卡采用 Chiplet 设 计,拥有 13 个小芯片,基于 3D 堆叠,包括 24 个 Zen4 CPU 内核,总共包含 128GB HBM3 显存和 1460 亿晶体管,性能上比此前的 MI250 提高了 8 倍,在功耗效率上提高了 5 倍。

中国首款基于 Chiplet 的 AI 芯片“启明 930”为北极雄芯开发,该芯片采用 12nm 工艺生产, 中央控制芯粒采用 RISC-V CPU 核心,可通过高速接口搭载多个功能型芯粒,并基于全国产 基板材料以及 2.5D 封装,做到算力可拓展,提供 8~20TOPS(INT8)稠密算力来适应不同场 景,目前已与多家 AI 下游场景合作伙伴进行测试。

2.2.Chiplet 市场规模快速成长

Chiplet 技术被视为“异构”技术的焦点,也是当下最被企业所认可的新型技术之一。2022 年 3 月,英特尔、AMD、Arm、高通、三星、台积电、日月光、Google Cloud、Meta、微软等 全球领先的芯片厂商共同成立了 UCIe 联盟,旨在建立统一的 die-to-die 互联标准,促进 Chiplet 模式的应用发展,目前联盟成员已有超过 80 家半导体企业,越来越多的企业开始研 发 Chiplet 相关产品。UCIe 在解决 Chiplet 标准化方面具有划时代意义,标志着产业化落地 开始。

中国首个原生 Chiplet 技术标准《小芯片接口总线技术要求》于 2022 年 12 月发布,该标准 有助于行业规范化、标准化发展,为赋能集成电路产业打破先进制程限制因素,提升中国集 成电路产业综合竞争力,加速产业进程发展提供指导和支持。 根据 Gartner 数据统计,基于 Chiplet 的半导体器件销售收入在 2020 年仅为 33 亿美元, 2022 年已超过 100 亿美元,预计 2023 年将超过 250 亿美元,2024 年将达到 505 亿美元,复 合年增长率高达 98%。超过 30%的 SiP 封装将使用芯粒(Chiplet)来优化成本、性能和上市 时间。MPU 占据 Chiplet 大部分应用应用场景,Omdia 预测 2024 年用于 MPU 的 Chiplet 约占 Chiplet 总市场规模的 43%。

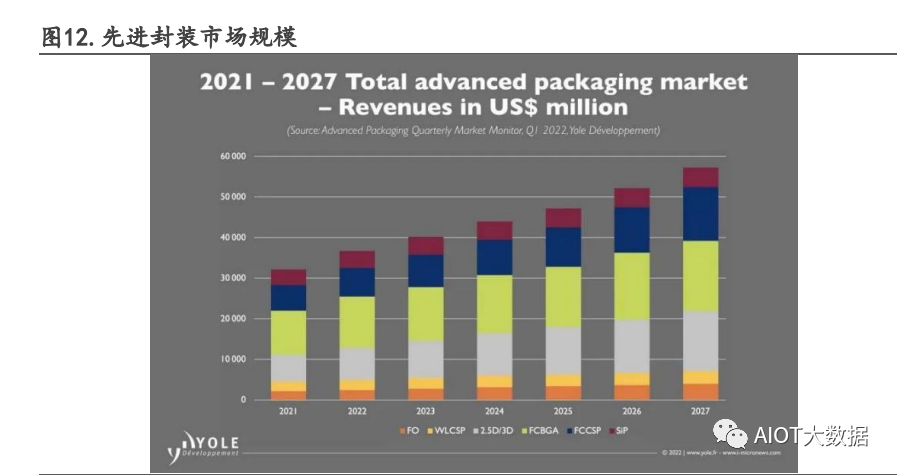

先进封装是实现 Chiplet 的前提,Chiplet 对先进封装提出更高要求。根据 Yole 数据统计, 2021 年先进封装市场收入达 321 亿美元,预计 2027 年将实现 572 亿美元,复合年增长率为 10%。Chiplet 的实现需要依托于先进封装,在芯片小型化的设计过程中,需要添加更多 I/O 与其他芯片接口,裸片尺寸有必要保持较大且留有空白空间,导致部分芯片无法拆分,芯片 尺寸小型化的上限被 pad(晶片的管脚)限制。并且单个晶片上的布线密度和信号传输质量 远高于 Chiplet 之间,要实现 Chiplet 的信号传输,就要求发展出高密度、大带宽布线的“先 进封装技术”。先进封装市场的快速发展为 Chiplet 市场的发展提供了技术基础。

3.龙头 IC 制造及封测厂加码布局 Chiplet

3.1.Chiplet 产业链:封测环节重要性大幅提高

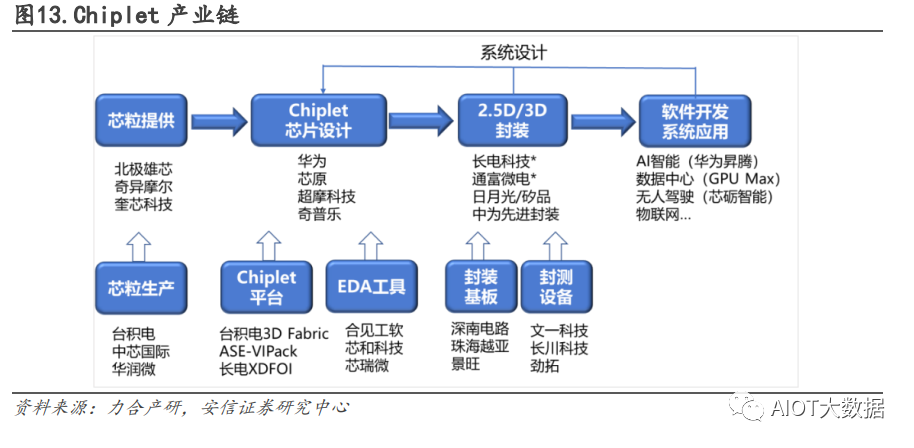

Chiplet 技术发展早期往往局限于企业内部独立研发和应用,且仅应用于一些高端产品,如 服务器和高性能计算等,组装和测试等方面仍存在技术瓶颈。随着 Chiplet 技术的不断成熟 和商业化推广,越来越多的芯片厂商、设计公司和封测厂开始使用 Chiplet 技术,Chiplet 的 商业化应用趋势也促进了整个芯片生态系统的升级和发展。随着 Chiplet 技术的发展, Chiplet 产业链各环节逐渐完善,即由 Chiplet 系统级设计、EDA/IP、芯粒(核心、非核心、 IO Die、Base Die)、制造、封测组成的完整 Chiplet 生态链。 Chiplet 产业链主链有四大环节,包括芯粒、芯片设计、封装生产和系统应用,支撑环节包 括芯粒生产、设计平台、EDA 工具、封装基板、封测设备等领域。从 Chiplet 产业链逻辑看,芯片设计和封装处于链条中心环节,且与后端系统应用紧密联动,而晶圆厂则被前置,成为 芯粒提供商的生产环节。

芯粒提供环节是指专业公司提供独立设计、优化和制造的芯粒给其他芯片制造商使用的过程。 这种模式可以提高芯片制造商的生产效率,加快产品推出时间,降低生产成本。传统的 IP 软 件企业将部分转向 IP 芯片化的芯粒提供商,芯粒提供商通常会提供成熟的 IP 和技术,使芯 片制造商可以更加专注于整个系统级设计和芯片集成。此外,芯粒提供商可以利用其专业知 识和技能,帮助芯片制造商优化设计,提高性能和降低功耗。 Chiplet 芯片设计环节需要考虑每个小型芯片的功能和性能要求,并确定芯片之间的接口和 通信方式。在这个环节中,芯片设计师需要利用各种 EDA 工具进行设计、验证和仿真,以确 保每个小型芯片都可以正确地集成在一起,同时满足整个芯片的性能要求和功能需求。此外, 芯片设计人员还需要考虑芯片的功耗、可靠性和安全性等因素,并制定相应的设计方案和测 试计划。芯片设计对于芯片的整体性能和功能有着至关重要的作用,因此芯片设计人员需要 具备深厚的电子设计自动化(EDA)知识和经验。

Chiplet 封测环节指将多个芯粒组装到一个芯片上,并进行测试和验证的过程。Chiplet 要 求高性能的芯粒互联,为先进封装技术带来了更多挑战。包括高密度互联带来的工艺带宽和 隔离问题,功率密度过高带来的散热问题,芯粒与封装高速连接的基板问题,以及对无源元 件集成封装问题等,同时 Chiplet 对封装产线的要求将从 2.5D、2.5+3D 逐渐过渡到 3D。另 外关键的测试技术也会影响 Chiplet 芯片的良率,包括大芯片的散热、供电、应力、信号完 整性(电磁场干扰)等。因此未来提升封测的技术水平对发展 Chiplet 至关重要。 Chiplet 技术已经成为现代系统设计的重要组成部分,广泛应用于云计算、人工智能、机器 学习、5G 通信、汽车和工业控制等领域。AMD 在 2019 年就发布了基于 Chiplet 模块化设计 的 EPYC 处理器;Intel 在 2022 年发布采用了 3D 封装的 Chiplet 技术的大型数据中心高性能 计算芯片 Ponte Vecchio,单个产品整合了 47 个小芯片,采用 5 种以上差异化工艺节点,集 成了超过 1000 亿个晶体管;苹果的 M1 Ultra 采用 Chiplet 技术将两个 M1 Max 通过芯片连 接在一起。国内以华为、寒武纪、壁仞科技等为代表的龙头企业,也有 Chiplet 产品上市。

3.2.全球巨头厂商加码布局 Chiplet 先进封装

目前全球封装技术主要由台积电、三星、Intel 等公司主导,主要是 2.5D 和 3D 封装。2.5D 封装技术已非常成熟,广泛应用于 FPGA、CPU、GPU 等芯片,目前是 Chiplet 架构产品主要的 封装解决方案。3D 封装能够帮助实现 3D IC,即晶粒间的堆叠和高密度互连,可以提供更为 灵活的设计选择。但 3D 封装的技术难度更高,目前主要有英特尔和台积电掌握 3D 封装技术 并商用。 台积电比三星、英特尔更早采用 Chiplet 的封装方式。台积电推出了 3DFabric,搭载了完备 的 3D 硅堆栈(3D Silicon Stacking)和先进的封装技术。3DFabric 是由台积电前端 3D 硅 堆栈技术 TSMC SoIC 系统整合的芯片,由基板晶圆上封装(Chip on Wafer on Substrate, CoWoS)与整合型扇出(Integrated Fan-Out, InFO)的后端 3D 导线连接技术所组成,能够 为客户提供整合异质小芯片(Chiplet)的弹性解决方案。该项技术先后被用于赛灵思的 FPGA、 英伟达的 GPU 以及 AMD 的 CPU。

Intel 主导的 2.5D 封装技术为 EMIB,使用多个嵌入式包含多个路由层的桥接芯片,同时内 嵌至封装基板,达到高效和高密度的封装。由于不再使用 interposer 作为中间介质,可以去 掉原有连接至 interposer 所需要的 TSV,以及由于 interposer 尺寸所带来的封装尺寸的限 制,可以获得更好的灵活性和更高的集成度。相较于 MCM 和 CoWoS 技术,EMIB 技术获得更高 的集成度和制造良率。英特尔对各种先进封装产品组合 (如 Foveros、EMIB 和 Co-EMIB) 的 投资是实施公司新领导层所公布的 IDM2.0 战略的关键。

三星也在积极投资先进的封装技术,以满足 HPC 应用在异质芯片整合的快速发展。2020 年 8 月,三星公布了 X Cube 3D 封装技术。在芯片互连方面,使用成熟的硅通孔 TSV 工艺。目前 X Cube 能把 SRAM 芯片堆叠在三星生产的 7nm EUV 工艺的逻辑芯片上,在更易于扩展 SRAM 容 量的同时也缩短了信号连接距离,提升了数据传输的速度。此后发布的 I-Cube 可以将一个 或多个逻辑 die 和多个 HBM die 水平放置在硅中介层,进行异构集成。

日月光凭借在 FOCoS 先进封装技术的布局,是目前在封测代工厂中唯一拥有超高密度扇出解 决方案的供应商。日月光的 FOCoS 提供了一种用于实现小芯片集成的硅桥技术,称为 FOCoSB(桥),它利用带有路由层的微小硅片作为小芯片之间的封装内互连,例如图形计算芯片 (GPU)和高带宽内存(HBM)。硅桥嵌入在扇出 RDL 层中,是一种可以不使用硅中介层的 2.5D 封 装方案。与使用硅中介层的 2.5D 封装相比,FOCoS-B 的优势在于只需要将两个小芯片连接在 一起的区域使用硅片,可大幅降低成本。

3.3.国内企业紧跟产业趋势,加快布局 Chiplet 先进封装

Chiplet 被视为中国与国外差距相对较小的先进封装技术,有望带领中国半导体产业在后摩 尔时代实现质的突破,因此,中国半导体企业紧跟产业趋势,纷纷走向 Chiplet 研发的道路。 中国三大封测企业长电科技、通富微电与华天科技都在积极布局 Chiplet 技术,目前已经具 备 Chiplet 量产能力。 长电科技推出的面向 Chiplet 小芯片的高密度多维异构集成技术平台 XDFOI可实现 TSVless 技术,达到性能和成本的双重优势,重点应用领域为高性能运算如 FPGA、CPU/GPU、AI、5G、自动驾驶、智能医疗等。XDFOI是一种以 2.5D TSV-less 为基本技术平台的封装技术, 在线宽/线距可达到 2μm/2μm 的同时,还可以实现多层布线层,以及 2D/2.5D 和 3D 多种异 构封装,能够提供小芯片(Chiplet)及异构封装的系统封装解决方案。目前长电先进 XDFOI 2.5D 试验线已建设完成,并进入稳定量产阶段,同步实现国际客户 4nm 节点多芯片系统集成 封装产品出货。

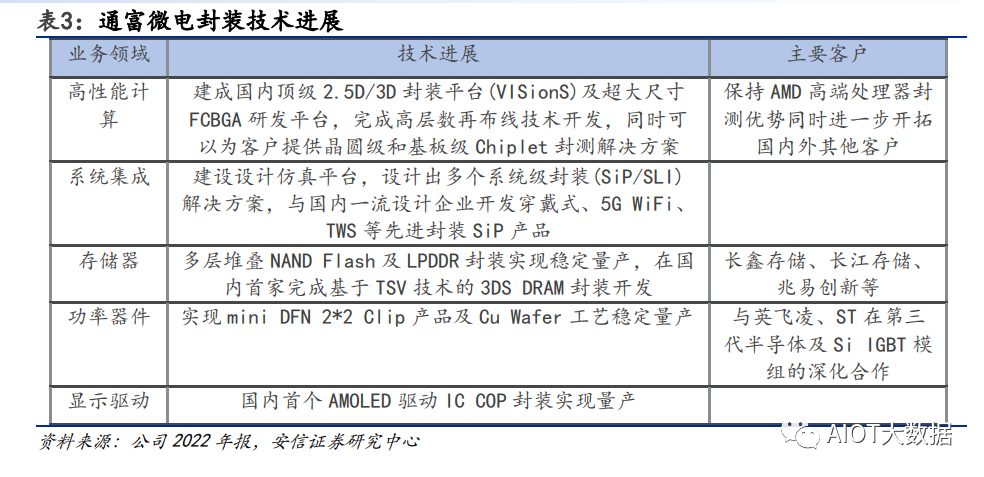

通富微电在先进封装方面公司已大规模生产 Chiplet 产品,7nm 产品已大规模量产,5nm 产 品已完成研发即将量产。公司目前已建成国内顶级 2.5D/3D 封装平台(VISionS)及超大尺寸 FCBGA 研发平台,完成高层数再布线技术开发。AMD 是最早研究并实现 Chiplet 应用的公司 之一,通富微电作为 AMD 在大陆唯一的封测合作伙伴,目前已经在 Chiplet 封装技术领域取 得市场先机,形成先发竞争优势。 华天科技已量产 Chiplet 产品,主要应用于 5G 通信、医疗等领域。华天科技已掌握 SiP、 FC、TSV、Bumping、Fan-Out、WLP、3D 等先进封装技术。华天科技目前已建立三维晶圆级封 装平台—3D Matrix,该平台由 TSV、eSiFo(Fan-out)、3D SIP 三大封装技术构成。

后摩尔时代,Chiplet 由于高性能、低功耗、高面积使用率以及低成本的优势,在延续摩尔 定律的“经济效益”方面被寄予厚望。Chiplet 芯片设计环节能够降低大规模芯片设计的门 槛,给中国集成电路产业带来巨大发展机遇。

4.重点公司分析

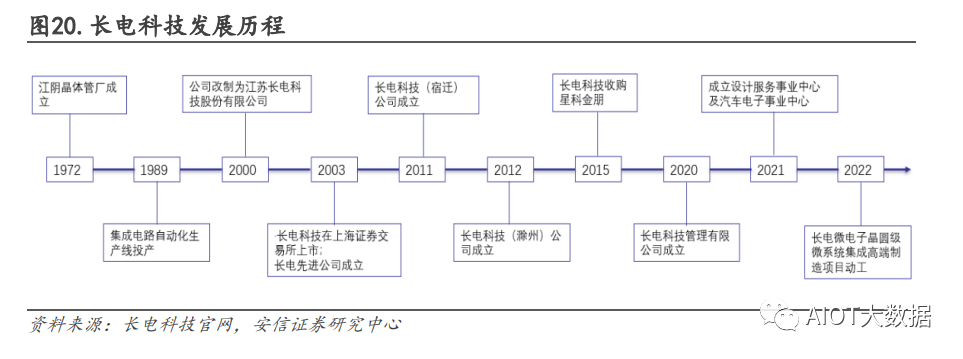

4.1.长电科技:国内先进封装龙头,23H2 有望迎周期拐点

长电科技成立于 1972 年,并于 2003 年在上交所上市,是全球领先的集成电路制造和技术服 务企业,在中国、韩国和新加坡设有六大生产基地和两大研发中心。公司提供全方位的芯片 成品制造一站式服务,包括集成电路的系统集成、设计仿真、技术开发、产品认证、晶圆中 测、晶圆级中道封装测试、系统级封装测试、芯片成品测试,并可向世界各地的半导体客户 提供直运服务。公司通过高集成度的晶圆级封装(WLP)、2.5D/3D 封装、系统级封装(SiP)、 高性能倒装芯片封装和先进的引线键合技术,覆盖了主流集成电路系统应用,包括网络通讯、 移动终端、高性能计算、车载电子、大数据存储、人工智能与物联网、工业智造等领域。

从公司的财务数据来看,公司营收规模不断扩大,归母净利润稳定提升。2020-2022 年,公 司营业收入分别约为 264.64 亿元、305.02 亿元和 337.62 亿元,归母净利润分别为 13.04 亿 元、29.59 亿元、32.31 亿元。公司近几年加速从消费类转向市场需求快速增长的汽车电子、 5G 通信、高性能计算、存储等高附加值市场的战略布局,持续聚焦高性能封装技术高附加值 应用,进一步提升核心竞争力。公司 2022 年实现营业收入 337.62 亿元,同比增长 10.7%; 归属于上市公司股东的净利润 32.3 亿元,同比增长 9.2%;资产负债率同比下降 6 个百分点, 主要系公司于 2022 年在汽车电子,高性能计算等领域完成了多项新技术开发及多家全球知 名客户新产品的量产导入;来自于汽车电子的收入 2022 年同比增长 85%,来自于运算电子的 收入同比增长 46%。 2023 年 Q1 公司实现营业收入 58.60 亿元,同比-27.99%;归母净利润 1.10 亿元,较去年同 比-87.24%;扣非归母净利润 0.56 亿元,较上年同比-92.80%。公司 Q1 业绩下滑主要系 23Q1 半导体行业景气周期继续下行,导致国内外客户需求继续下降,订单减少。从盈利能力来看, 由于公司产能利用率大幅下滑,2023Q1盈利能力也有所下滑,毛利率环比-5.20pct至11.84%, 净利率环比-7.69%至 1.88%。23Q1 在下游需求大幅下降的背景下,公司汽车电子业务仍然保 持高速增长。随着公司产品结构的优化,公司业绩有望复苏。

公司 2022 年度营业收入按市场应用领域划分来看,通讯电子占比 39.3%、消费电子占比 29.3%、 运算电子占比 17.4%、工业及医疗电子占比 9.6%、汽车电子占比 4.4%, 电子元器件采购网 与去年同期相比消费 电子下降 4.5 个百分点,运算电子增长 4.2 个百分点,汽车电子增长 1.8 个百分点。在测试 领域,公司引入 5G 射频,车载芯片,高性能计算芯片等更多的测试业务,相关收入同比增长 达到 25%。

公司在 Chiplet 领域处于领先地位,目前 XDFOI Chiplet 高密度多维异构集成系列工艺已 按计划进入稳定量产阶段,同步实现国际客户 4nm 节点多芯片系统集成封装产品出货,最大 封装体面积约为 1500mm²的系统级封装。该技术是一种面向 Chiplet 的极高密度、多扇出型 封装高密度异构集成解决方案,其利用协同设计理念实现了芯片成品集成与测试一体化,涵 盖 2D、2.5D、3D 集成技术。经过持续研发与客户产品验证,公司 XDFOI不断取得突破,已 在高性能计算、人工智能、5G、汽车电子等领域应用,为客户提供了外型更轻薄、数据传输 速率更快、功率损耗更小的芯片成品制造解决方案,满足日益增长的终端市场需求。

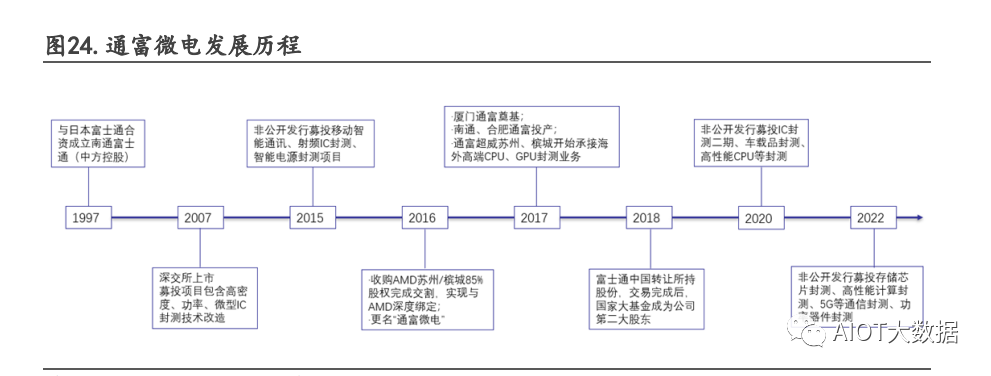

4.2.通富微电:深度合作 AMD,AI+Chiplet 打开成长空间

通富微电成立于 1997 年,并于 2007 年在深交所上市,是集成电路封装测试服务提供商,为 全球客户提供设计仿真和封装测试一站式服务。2014 年以来,通富微电相继在南通、合肥、 厦门等地投资建厂,目前,通富微电相继投资了崇川总部工厂、南通通富、通富通科、合肥 通富、厦门通富、通富超威苏州、通富超威槟城七大生产基地,员工总数 2 万多人,生产总 面积超过 100 万平米。2021 年全球 OSAT 中通富微电位列第五,先进封装方面位列第七。公 司的产品、技术、服务全方位涵盖人工智能、高性能计算、大数据存储、显示驱动、5G 等网 络通讯、信息终端、消费终端、物联网、汽车电子、工业控制等领域。

2016 年,通富微电通过并购通富超威苏州和通富超威槟城,与 AMD 形成了“合资+合作”的 强强联合模式,深度锁定了 AMD 供应链并占据 AMD 封测订单的大部分份额。由于通富超威苏 州和通富超威槟城前身为 AMD 内部封测厂,熟悉 AMD 产品的生产及管理流程,对于 AMD 而言, 通富超威苏州及通富超威槟城在产品验证、产品质量、新产品开发时间、业务对接效率等方 面具有优势。收购以来,通富微电与 AMD 的合作不断深化,为 AMD 第一大封测产品供应商, 未来随着大客户资源整合渐入佳境,产生的协同效应将带动整个产业链持续受益。 从公司的财务数据来看,公司业务发展迅速,收入规模不断扩大,市场份额持续提升。2020- 2022 年,公司营业收入分别约为 107.69 亿元、158.12 亿元和 214.29 亿元,归母净利润分 别为 3.38 亿元、9.57 亿元、5.02 亿元。在全球前十大封测企业中,公司营收增速连续 3 年 保持第一。公司通过积极调整产品业务结构,加大市场调研与开拓力度,凭借 7nm、5nm、FCBGA、 Chiplet 等先进技术优势,不断强化与 AMD 等行业领先企业的深度合作,巩固和扩大先进产 品市占率,营收稳定提升。公司 2022 年归母净利润有所下滑,主要系集成电路行业景气度下 行,部分终端产品需求疲软,导致公司产能利用率及毛利率下降;同时公司加大 Chiplet 等 先进封装技术创新研发投入,研发费用增加,导致利润下降。

2023 年 Q1 公司实现营业收入 46.42 亿元,同比+3.11%;归母净利润 0.05 亿元,较去年同比 -97.24%;扣非归母净利润-0.46 亿元,较上年同比-131.72%。公司 Q1 业绩有所下滑,主要 系受欧洲地缘政治风险升级、美国持续高通胀等外部因素影响,集成电路行业景气度下降, 终端厂商进去库周期导致封测行业订单出现下滑。从盈利能力来看,2023Q1 盈利能力有所下 滑,毛利率 9.45%,环比-4.45pct,主要系公司产能利用率下降所致。

Chiplet 技术方面,公司通过在多芯片组件、集成扇出封装、2.5D/3D 等先进封装技术方面的 提前布局,可为客户提供多样化的 Chiplet 封装解决方案并已量产,基于 ChipLast 工艺的 Fan-out 技术,实现 5 层 RDL 超大尺寸封装(65×65mm),超大多芯片 FCBGAMCM 技术,实现 最高 13 颗芯片集成及 100×100mm 以上超大封装。目前,公司技术布局进展顺利,已开始大 规模生产 Chiplet 产品,工艺节点方面 7nm 产品实现量产,5nm 产品完成研发。受益于公司 在封测技术方面的持续耕耘,目前公司与 AMD、NXP、TI、英飞凌、ST、联发科、展锐、韦尔 股份、兆易创新、长鑫存储、长江存储、集创北方及其他国内外各细分领域头部客户建立了 良好的合作关系,2021 年,国内客户业务规模增长超 100%。

4.3.华天科技:业绩静待周期复苏,Chiplet 布局业内领先

华天科技成立于 2003 年 12 月 25 日,2007 年 11 月 20 日在深交所成功上市。公司主要从事 半导体集成电路、半导体元器件的封装测试业务,主要为客户提供封装设计、封装仿真、引 线框封装、基板封装、晶圆级封装、晶圆测试及功能测试、 物流配送等一站式服务。目前公 司集成电路封装产品主要有 DIP/SDIP、SOT、SOP、SSOP、TSSOP/ETSSOP、QFP/LQFP/TQFP、 QFN/DFN、BGA/LGA、FC、MCM(MCP)、SiP、WLP、TSV、Bumping、MEMS 等多个系列,产品主要 应用于计算机、网络通讯、消费电子及智能移动终端、物联网、工业自动化控制、汽车电子 等电子整机和智能化领域。2022 年公司持续加大研发投入,完成了 3D FO SiP 封装工艺平 台、基于 TCB 工艺的 3D Memory 封装技术的开发;双面塑封技术、激光雷达产品完成工艺验 证;基于 232 层 3D NAND Flash Wafer DP 工艺的存储器产品、长宽比达 7.7:1 的侧面指纹、 PAMiD 等产品均已实现量产;与客户合作开发 HBPOP 封装技术。

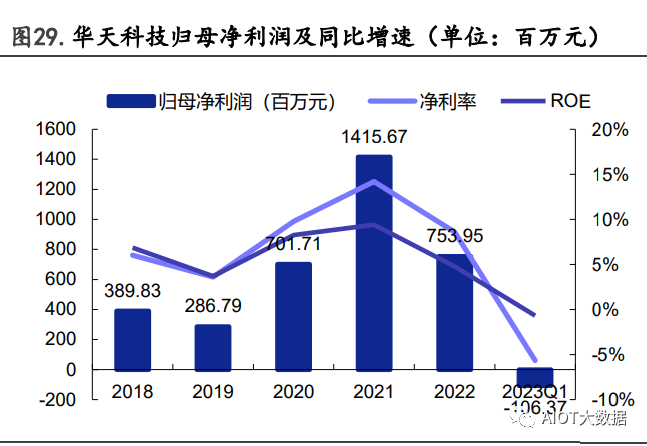

从公司的财务数据来看,公司业务发展迅速,收入规模不断扩大,市场份额持续提升。 2020- 2022 年,公司营业收入分别约为 83.82 亿元、120.97 亿元和 119.06 亿元,归母净利润分别 为 7.02 亿元、14.16 亿元、7.54 亿元。公司 2022 年营收与归母净利润同比有所下滑,主要 由于终端市场产品需求下降,集成电路行业景气度下滑。从盈利能力来看,公司 2022 年毛利 率 16.84%,同比下降 7.77 个百分点;公司净利润率 8.59%,同比下滑 5.62 个百分点。 2023 年 Q1 公司实现营业收入 22.39 亿元,同比-25.56%;归母净利润-1.06 亿元,较去年同 比-151.43%;扣非归母净利润-1.82 亿元,较上年同比-222.67%。公司 Q1 业绩下滑主要系地 缘政治冲突、经济发展放缓等因素导致半导体市场终端消费动力不足。从盈利能力来看,由 于公司产能利用率大幅下滑,2023Q1 盈利能力也大幅下滑,毛利率环比-12.85pct 至 3.99%, 净利率环比-14.25%至-5.66%。公司在市场需求减弱、去库存等不利因素的情况下,积极优化客户结构,2022 年公司导入客户 237 家,通过 6 家国内外汽车终端及汽车零部件企业审核, 引入 42 家汽车电子客户,涉及 202 个汽车电子项目。同时公司积极推进募集资金投资项目 及韶华科技等新生产基地建设。随着半导体行业的复苏,公司产业规模有望进一步扩大。

在 Chiplet 领域,公司实现了 3D FO SiP 封装工艺平台的开发,现已具备由 TSV、eSiFo、3D SiP 构成的最新先进封装技术平台——3D Matrix。其中晶圆级 eSiFO 主要应用于 Fan-out 封 装上,其优势包括硅基板,翘曲小、应力低的高可靠性,生产周期短、工艺设备小的低成本、 高集成度、系统级封装。公司基于 eSiFO 结合 TSV 技术,开发了 eSinC 技术。在 eSiFO 技术 的基础上,可以通过 TSV、Bumping 等晶圆级封装的技术,实现 3D SiP 的封装,为多芯片的 异质异构集成提供了可能性。公司目前 Chiplet 技术已经实现量产,主要应用于 5G 通信、医 疗、物联网等领域。

4.4.甬矽电子:聚焦先进封装,Chiplet 前景可期

甬矽电子成立于 2017 年,于 2022 年在上海证券交易所上市。公司主要从事集成电路的封装 和测试业务。公司成立之初就聚焦集成电路封测业务中的先进封装领域,车间洁净等级、生 产设备、产线布局、工艺路线、技术研发、业务团队、客户导入均以先进封装业务为导向, 公司全部产品均为中高端先进封装形式,封装产品主要包括“高密度细间距凸点倒装产品(FC 类产品)、系统级封装产品(SiP)、扁平无引脚封装产品(QFN/DFN)、微机电系统传感器(MEMS)” 4 大类别。公司自 2017 年成立以来,凭借出色的产品质量控制和服务能力,在短时间内迅速 形成量产并进入恒玄科技、晶晨股份、联发科等顶尖集成电路设计企业供应链,特别在射频 芯片封测领域具备较强的竞争力。

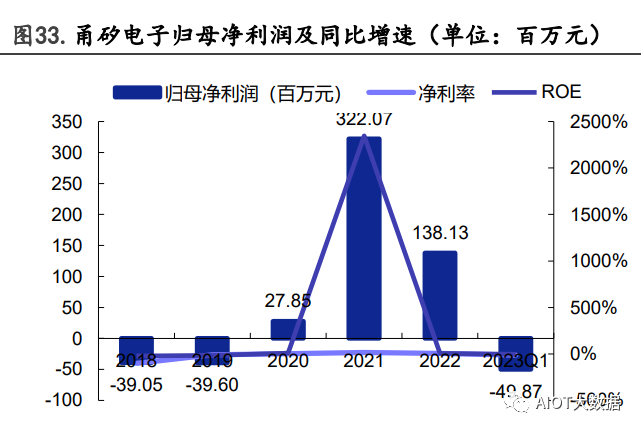

从公司财务数据来看,得益于集成电路国产化、智能化以及 5G、新基建等新兴应用的驱动、 下游客户旺盛的市场需求以及公司市场地位和品牌形象的提升,公司营业收入、营业毛利逐 年稳定上升。2020-2022 年,公司营业收入分别约为 7.48 亿元、20.55 亿元和 21.77 亿元, 归母净利润分别为 0.28 亿元、3.22 亿元、1.38 亿元。公司 2022 年营收缓慢增长主要系在 市场需求减弱、行业整体进入去库存周期等不利因素的情况下,公司持续优化客户结构,与 多家细分领域头部客户建立战略合作伙伴关系。公司 2019 年-2021 年,主营业务毛利率逐年 稳步上升,2022 年毛利率有所下降主要系国内消费电子等市场需求萎缩,公司部分产品的销 售单价有所下降,SiP 类产品、QFN 类产品毛利率有所下降。

2023 年 Q1 公司实现营业收入 4.25 亿元,同比-26.86%;归母净利润-0.50 亿元,较去年同 比-170.04%;扣非归母净利润-0.69 亿元,较上年同比-211.12%。公司 Q1 业绩下滑主要系 2023Q1,终端市场整体延续了 2022 年下半年的疲软状态,下游客户整体处于库存调整状态, 整体订单仍较为疲软。从盈利能力来看,受 1 月份春节假期、订单整体下滑等影响,公司整 体产能利用率有所下滑,毛利率环比-13.52%至 8.39%。此外,公司二期项目有序推进,公司 人员规模持续扩大,人员支出及二期筹建费用增加,使得管理费用同比增长 75.06%,23Q1 归 母净利润同比下滑 170.04%。

从公司营收结构来看,2022 年系统级封装产品(SIP)实现销售收入 122,524.49 万元,较上 年同期增长 7.93%,销售成本同比增长 25.16%,毛利率同比下降 10.45 个百分点。扁平无引 脚封装产品(QFN/DFN)实现销售收入 63,184.17 万元,较上年同期减少 10.10%,销售成本 同比增加 11.31%,毛利率同比下降 16.92 个百分点。高密度细间距凸点倒装产品(FC 类产 品)实现销售收入 29,206.06 万元,较上年同期增长 58.64%,销售成本同比增长 66.82%,毛 利率同比下降 3.36 个百分点。微电机系统传感器(MEMS)实现销售收入 537.12 万元,较上 年同期减少 70.54%,销售成本同比减少 74.56%,毛利率同比上升 13.12 个百分点。

Chiplet 模式能满足现今高效能运算处理器的需求,而 SiP 等先进封装技术是 Chiplet 模式 的重要实现基础。公司在 SiP 领域具备丰富的技术积累,通过实施晶圆凸点产业化项目布局 “扇入型封装”(Fan-in)、“扇出型封装”(Fan-out)、2.5D、3D 等晶圆级和系统级封装应用 领域,并为进一步拓展异构封装领域打下基础。。同时,公司已经掌握了系统级封装电磁屏蔽 (EMI Shielding)技术、芯片表面金属凸点(Bumping)技术,并积极开发 7 纳米以下级别 晶圆倒装封测工艺、高密度系统级封装技术、硅通孔技术(TSV)等,为 Chiplet 技术储备了 充足的技术基础。

4.5.芯原股份:发展先进工艺,以 Chiplet 拓展广阔市场

芯原股份成立于 2001 年,于 2020 年在上海证券交易所上市。芯原股份是一家依托自主半导 体 IP,为客户提供平台化、全方位、一站式芯片定制服务和半导体 IP 授权服务的企业。在 芯原独有的 Silicon Platform as a Service 经营模式下,通过基于公司自主半导体 IP 搭建的技术平台,可在短时间内打造出从定义到测试封装完成的半导体产品。公司的业务范围 覆盖消费电子、汽车电子、计算机及周边、工业、数据处理、物联网等行业应用领域。

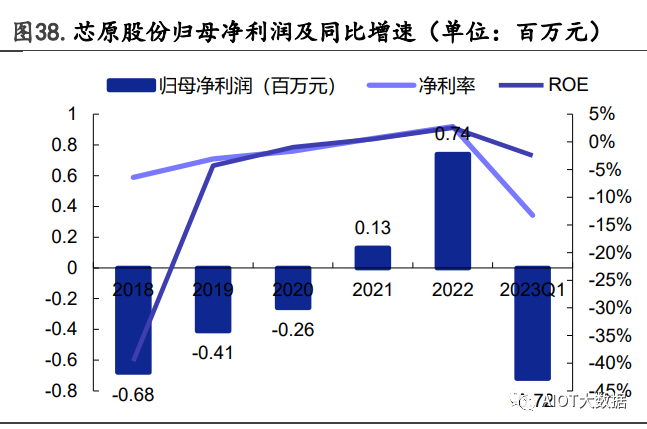

从公司的财务数据来看,2022 年度,公司实现营业收入 26.79 亿元,同比增长 25.23%,其中 半导体 IP 授权业务(包括知识产权授权使用费收入、特许权使用费收入)实现营收 8.93 亿 元,同比增长 26.57%;一站式芯片定制业务(包括芯片设计业务收入、量产业务收入)实现 营收 17.80 亿元,同比增长 24.19%。公司 2022 年实现归母净利润 0.74 亿元,同比增长 455.31%。公司 2022 年度在半导体产业下行压力增大的产业背景下,实现业绩稳定增长,主 要得益于公司独特商业模式,即原则上无产品库存的风险,无应用领域的边界,以及逆产业 周期的属性等。公司 2022 年在手订单金额 21.50 亿元,其中一年内(2023 年)转化的在手 订单金额 16.95 亿元,占比 78.82%,在手订单饱满。 2023 年 Q1 公司实现营业收入 5.39 亿元,同比-3.77%;归母净利润-0.72 亿元,较去年同比 -2280.25%。公司在手订单充足,截至 2023 年一季度末,公司在手订单金额为 18.10 亿元。 公司 Q1 业绩下滑主要系知识产权授权业务与客户项目启动安排相关,单季度收入存在一定 季度性波动。从盈利能力来看,由于公司知识产权授权业务受到客户项目启动安排相关等因 素影响单季度收入有所波动,导致高毛利率的半导体 IP 授权业务收入及收入占比下降,毛 利率环比-9.98%至 38.94%。公司一站式芯片定制业务毛利率同比有所提升,其中芯片设计业 务毛利率 5.31%,芯片量产业务毛利率 26.92%。

Chiplet 可从多维度降低芯片设计及制造成本,公司深耕 Chiplet 技术,大算力时代有望持 续受益。随着半导体工艺制程推进,晶体管尺寸越来越逼近物理极限,所耗费的研发时间及 成本越来越高,Chiplet 技术通过大幅提高大芯片良率、降低设计复杂度和成本、芯片制造 成本,具有极大的发展潜力。公司基于“IP 芯片化,IP as a Chiplet”和“芯片平台化, Chiplet as a Platform”两大设计理念,推出了基于 Chiplet 架构所设计的高端应用处理 器平台,目前该平台 12nm SoC 版本已完成流片和验证,并正在进行 Chiplet 版本的迭代。 公司持续推进 Chiplet 技术产业化,加入 UCIe 联盟,强化在自动驾驶、数据中心和平板电脑 领域的布局,有望在大算力时代持续受益。

4.6.长川科技:国内半导体测试设备领先厂商,Chiplet+先进封装打开发展机遇

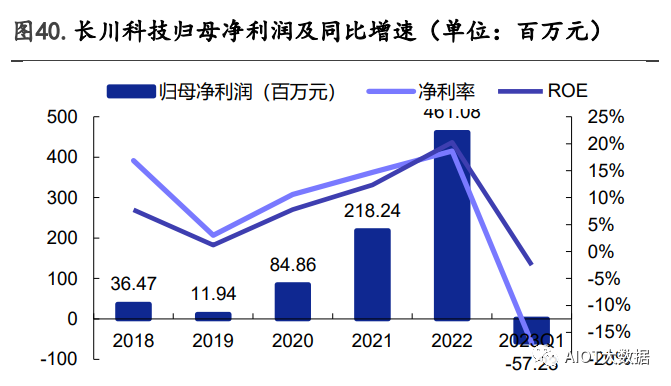

长川科技成立于 2008 年,是国内领先的集成电路测试设备及自动化解决方案供应商。公司 目前主营产品包含测试机、分选机和探针台,全面布局后道测试设备,并通过并购 STI 进入 前道晶圆检测领域。目前,公司生产的集成电路测试机和分选机产品已获得长电科技、 华天 科技、通富微电、士兰微、华润微电子、日月光等多个一流集成电路企业的使用和认可。 从公司的财务数据来看, 公司近几年营收以及归母净利润呈现快速提高趋势,营收从 2018 年的 2.16 亿元提高到 2022 年的 25.77 亿元,归母净利润从 2018 年的 0.36 亿元提高到 2022 年的 4.61 亿元。2022 年公司全年营收及归母净利润大幅提高,主要系公司坚持研发创新, 丰富产品矩阵,稳步扩大市场份额。同时公司产品结构优化,高端品类收入占比持续上升, 也推动了业绩的增长。另外,公司于 2022 年通过了发行股份购买资产收购长奕科技(马来 西亚 Exis)的审批。EXIS 主要从事集成电路分选设备的研发、生产和销售,核心产品主要 为转塔式分选机,有助于长川科技丰富产品类型,实现重力式分选机、平移式分选机、转塔 式分选机的产品全覆盖。

2023Q1 公司实现收入 3.20 亿元,同比-40.48%,环比-61.12%;实现归母净利润-0.57 亿元, 同比-180.50%,环比-141.91%。公司 Q1 营收同比大幅下滑,主要系封测厂稼动率承压致使其 资本开支下修,公司订单下滑导致营收与净利润均大幅下滑。公司目前是国内数字测试机领 域龙头供应商,在数字测试机领域已完成 D9000K 产品研发,随着 SoC 测试机在市场持续放 量,公司与大客户合作加深,公司业绩有望复苏。

从收入结构来看,2022 年公司分选机、测试机营业收入分别为 12.55 亿元、11.16 亿元,同 比分别+34.04%、+128.18%,毛利率分别为 44.62%、68.96%,同比分别+1.97pct、+1.29pct, 各项业务营收大幅提高,高毛利率的测试机业务占比 43.32%,份额逐步提升。

Chiplet 技术的兴起,拉动测试产业整体需求。在 CP 测试环节,因为 Chiplet 封装成本高, 为确保良率、降低成本,需要在封装前对每一颗芯片裸片进行 CP 测试,相较于 SoC,Chiplet 对芯片的 CP 测试需求按照芯片裸片数量成倍增加;在 FT 测试环节,随着 Chiplet 从 2D 逐 渐发展到 2.5D、3D,测试的难度提升,简单测试机减少,复杂测试机增加。经过多年持续技 术创新,公司测试机和分选机在核心性能指标上已达到国内领先、接近国外先进水平。公司 生产的集成电路测试机和分选机等产品已获得长电科技、华天科技、通富微电、士兰微、华 润微电子、日月光等多个一流集成电路厂商的使用和认可。随着 Chiplet 方案的引入,测试 设备将伴随下游芯片封测数量、价值量提升,有望迎来需求快速起量。

4.7.华兴源创: 半导体检测设备快速放量,充分受益 Chiplet 技术发展

华兴源创成立于 2005 年 6 月,于 2019 年成为全国第一家在科创板上市的企业。公司是国内 领先的检测设备与整线检测系统解决方案提供商,主要从事平板显示及集成电路的检测设备 研发、生产和销售。2018 年公司进军半导体检测,2020 年公司通过并购欧立通进军智能穿戴 领域。公司产品主要应用于 LCD 与 OLED 平板显示及微显示、半导体、可穿戴设备、新能源 汽车等行业,为客户提供从整机、系统、模块、SIP、芯片各个工艺节点的自动化测试设备。

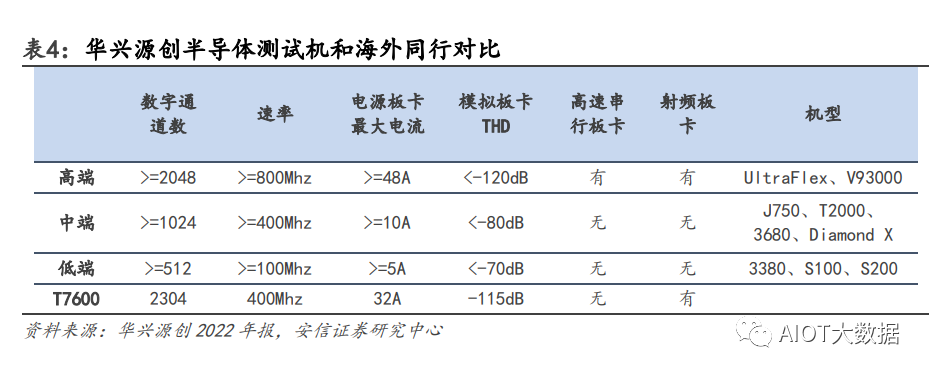

从公司产品结构来看,公司在平板和半导体检测板块产品十分丰富,在平板检测业务保持业 内领先水平,MiniLED、Micro-LED 及 Micro-OLED 等新一代显示检测技术储备不断升级;半 导体检测业务包括测试机、分选机、AOI 缺陷检测设备在内的多个标准设备也陆续进入量产。 消费电子检测及自动化设备业务是目前收入主要来源,半导体检测设备业务份额有望继续提 升。根据公司公告,2022 年公司消费电子检测及自动化设备业务营收 15.08 亿元,同比增长0.92%,占总营收 64.98%;半导体检测设备制造业务营收 5.66 亿元,同比增长 35.55%,占总 营收 24.39%。 在半导体测试机上,公司是全球为数不多的可以同时自主研发 ATE 架构 SOC 测试机和 PXIE 架构射频和系统模块测试机的企业,主打 SOC、射频测试机以及 SiP 测试解决方案。在 SoC 测试机上,公司自主研发的 T7600 系列测试机频率速率达到 400MHZ,部分技术参数已经达到 行业内公认的中档 SOC 测试机水平,直接对标泰瑞达的 J750-HD,目前已经获得下游知名 CIS、 MCU 以及指纹识别等芯片客户订单。

从公司的财务数据来看,公司业务发展迅速,收入规模不断扩大,市场份额持续提升。 2020- 2022 年,公司营业收入分别约为 16.77 亿元、20.20 亿元和 23.20 亿元,归母净利润分别为 2.65 亿元、3.14 亿元、3.31 亿元。公司 2022 年业绩稳定增长主要系半导体检测设备产品的 需求稳步扩大,同时公司进一步优化了成本结构,使成本增长远低于公司收入增长。从盈利 能力来看,公司 2022 年毛利率 52.08%,同比下降 0.96 个百分点;公司净利润率 14.27%,同 比下滑 1.27 个百分点,公司盈利水平总体稳定在高位。 2023Q1 公司实现营收 3.59 亿元,同比-3.91%;实现归母净利润 0.27 亿元,同比增长-34.41%。 公司 Q1 营收同比小幅下滑,主要受制于消费电子行业景气下行;净利润下滑明显主要系费 用率提高所致,Q1 期间费用率为 52.03%,同比+4.93%。随着消费电子景气度复苏、Micro OLED 检测设备放量以及半导体检测设备出货量提高,公司业绩有望进一步增长。

Chiplet 技术代表的先进封装工艺,是将多颗芯片整合成一个半导体系统的先进封装技术。 Chiplet 技术的广泛应用,亦带动了下游厂商对配套测试设备的需求。由于 Chiplet 技术实 现了芯片的模组化和系统级整合,因此针对系统级芯片的检测需要满足覆盖功能多、差异化 程度高的需求,这也导致了检测环节的耗时增长。华兴源创目前推出的基于 PXIE 架构的测试机搭配 EP3000 分选机的综合测试解决方案为歌尔微电子等客户提供了高效测试解决方案, 可满足客户的先进封装需求。

- 中国 Chiplet 芯粒产业全景整理:设计公司、封装专利、技术工艺及相关企业2025-08-28

- 亿配芯城接入DEEPSEEK AI 大模型,让芯片采购更灵活2025-04-25

- 史上最大芯片出炉,专为AI设计2024-11-26

- 赛普拉斯USB-C解决方案助力ELKA推出全球首款HDMI Alt 模式线缆2024-11-08

- AI在喧嚣中一路走来,2017年人工智能领域都收获了什么?2024-10-14

- AMD处理器助力 工业嵌入式设备应用更广泛2024-10-07